比较器offset论文研读

比较器offset论文研读

笔者最近在做比较器的相关电路,需要仿真offset,如果 $V_{FS}=1V$ ,并且是10Bits的ADC的话,则要求offset满足 $V_{OS}<\frac{1}{2}LSB=0.48mV$ 。因此仿真计算比较器的offset有重大意义。

遗憾的是笔者在某宝买的虚拟机没有mis模型,跑不了蒙卡,因此笔者也就萌生出了手算offset的想法,故也就有了本文。

offset定义

offset定义:当比较器输出达到 $\frac{V_{DD}}{2}$ 时,输入端 $V_{in}$ 和 $V_{ip}$ 的差值。

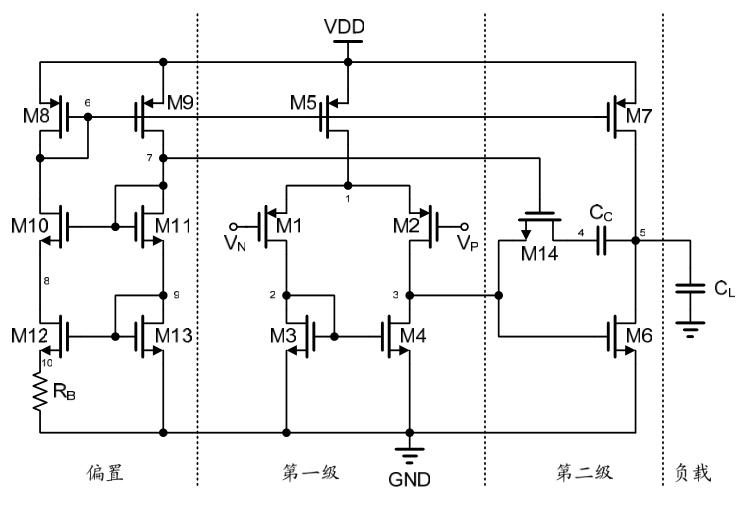

首先offset由系统失配和随机失配带来。系统失配指的是电路本身设计所带来的,如下图所示:

系统失配

在图1的二级运放电路图中我们需要保证M3、M4、M6的 $V_{GS}$ 一致,即若实际直流工作点存在偏差的话则会贡献有一部分offset,本文重点分析random mismatch带来的offset。

随机失配

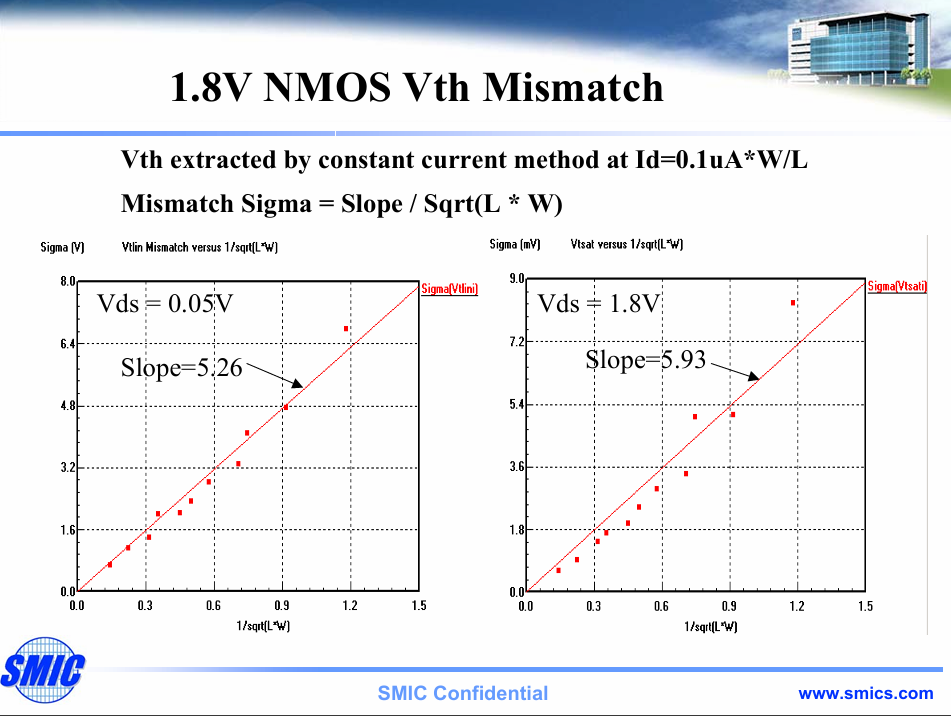

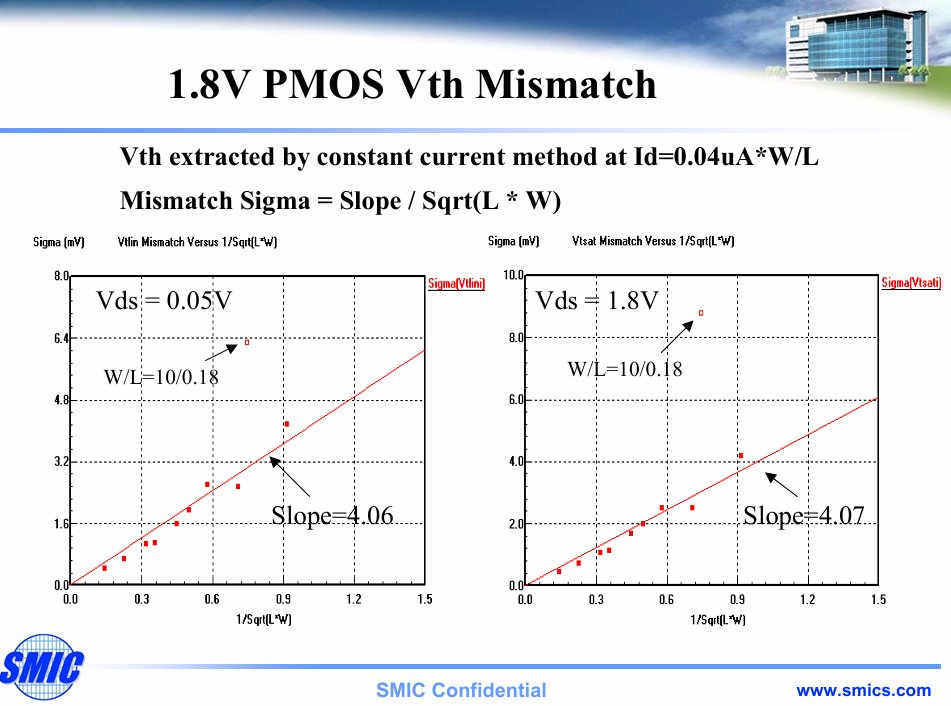

在实际芯片生产过程中,存在梯度效应,简单来说就是工艺生产的不均匀性,所以可能存在沿某一方向某一指标的持续恶化,例如沿东南方向电子迁移率持续降低。这和Layout时尽量对角对称的初衷差不多。本文重点分析关于导通电压 $V_{TH}$ 和迁移率 $\mu$ 的mismatch,结合文中的结论,它近似满足如下分布:

其中 $A_{Vt}$ 为制造工艺决定的常数,$D$ 为chip中各pair管子之间的距离。

其中的具体参数可以参考下方链接中的文档,也可参考下方的图2图3所示:

手算offset

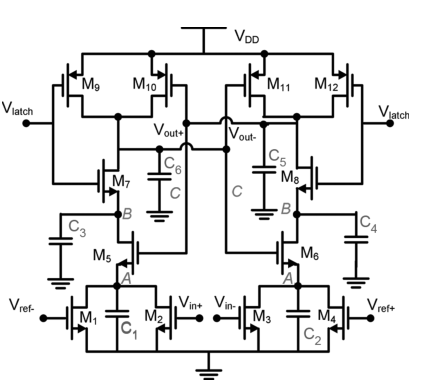

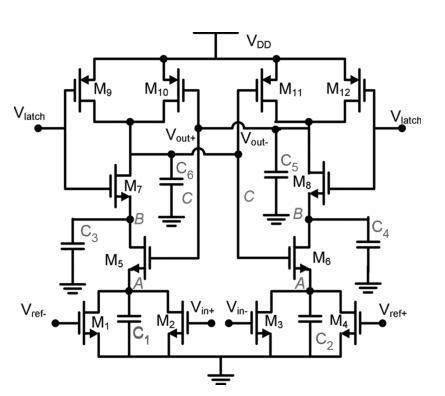

OK回归主题,开始计算offset。本文以图4所示的Lewis-Gray型动态比较器结构来分析:

思路十分简单:从KCL出发,将M5-M6 pair,M7-M8 pair,M10-M11 pair的电流与M1-M2、M3-M4的电流关联起来,同时通过KCL做差求解 $V_{OS} = V_{in+} - V_{in-}$ 。

思路就是这样,下面是具体的分析过程,为了考虑 $V_{TH}$ 和迁移率 $\mu$ 的mismatch,我们考虑如下形式引入微小变化量,以M5-M6 pair为例:

考虑如下KCL方程:

进而通过求解 $V_{in+} - V_{in-}$ 求解 $V_{OS}$。

阈值电压和迁移率mismatch的计算结果

本文基于如下简化分析,讨论:

选择 $V_{latch}$ 刚达到 $V_{DD}$ 时的时刻来分析;所有管子具有相同的栅长 $L$ ;M1-M4具有相同的尺寸;同时各管子工作在如下工作区:

| 管子 | 工作区 |

|---|---|

| M1-M4 | 三极管区 |

| M5-M6 | 饱和区 |

| M7-M8 | 三极管区 |

| M10-M11 | 饱和区 |

其中M9和M12的mismatch影响可以忽略不记。同时考虑 $V_{TH}$ 和 $\mu$ 的失配服从Guassian分布,则各pair管子所贡献的 $V_{OS}$ 的方差满足下列式子:

考虑到每对pair的管子的mismatch是独立分布的,因此总的 $V_{OS}$ 满足下式:

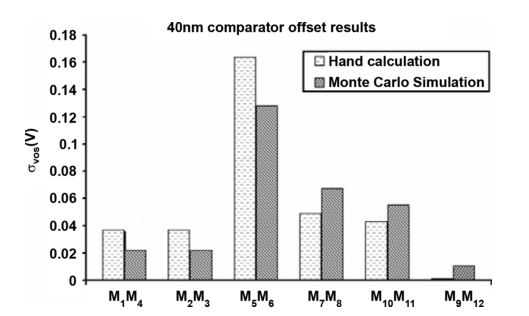

下面这张图是40nm下比较器的offset的蒙卡仿真结果与手算结果的比较:

总体符合拉扎维先生在《The Design of a Comparator》一文中提出的结论:在一个典型的设计中,当把M7和M8之间的失调等效到输入端时,需要先除以一个大约为 $A_{v}=10$ 的因子(第二阶段的增益倍率);而当M10、M11导致的失调等效到输入端时,需要除以一个大约为10的因子,这是因为考虑到了M10、M11管只有在最后两个阶段的时候才导通。

但是拉扎维先生论文中比较器的电路和本文讨论的略有不同。

寄生电容mismatch的计算结果

此处先给出一些典型值,1fF的电容失配可能会带来输出结点几十毫伏的输入参考失配电压。其中包含寄生电容的比较器结构图如下图所示:

为简化分析,只讨论输出节点的寄生电容 $C_{5}$ 和 $C_{6}$ ,同时忽略其他电容的分流作用,因此得到如下方程:

同时考虑 $C_{5}$ 和 $C_{6}$ 之间存在微小失配,即有下式:

进而得到:

总结

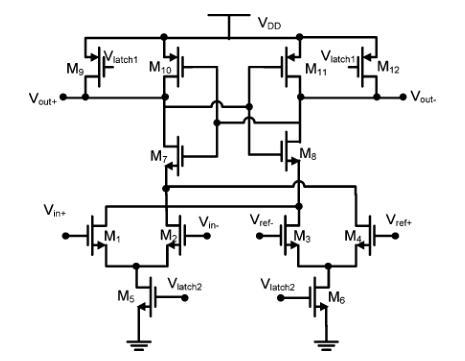

调整为下图所示的拓扑结构可以优化offset表现:

不愧是TCAS-I的文章,读起来就是通畅。

参考文献:

Analyses of Static and Dynamic Random Offset Voltages in Dynamic Comparators