四川大学微电子2022级大三下期末考试植树

IC设计基础

1.五管OTA小信号电路+增益求解

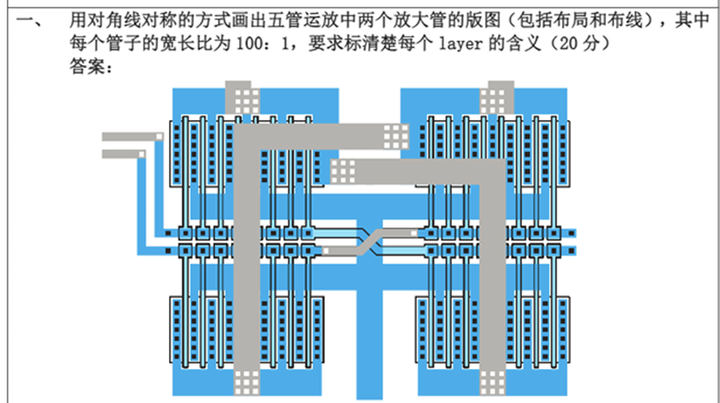

2.绘制二级运放中宽长比为100:1的输入对管的版图,同时标清楚每个layer的含义

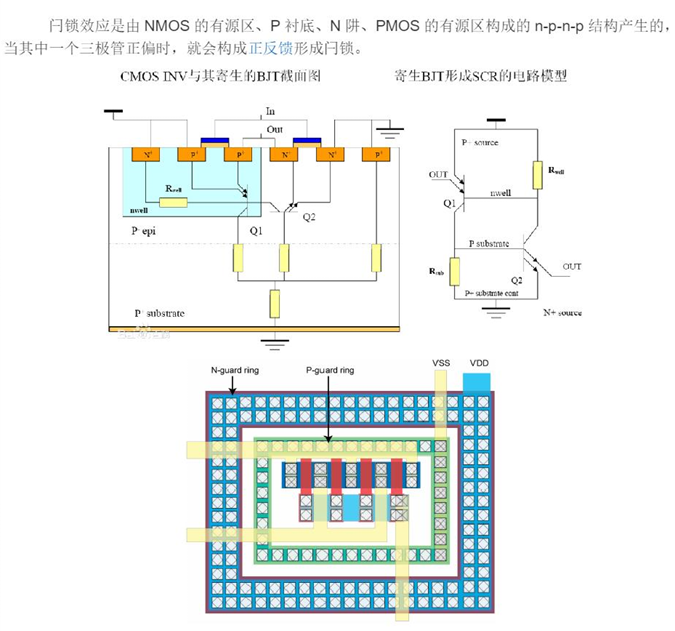

3.通过CMOS工艺图和寄生等效放大电路图简述闩锁效应的成因,以及如何减小闩锁效应的方法

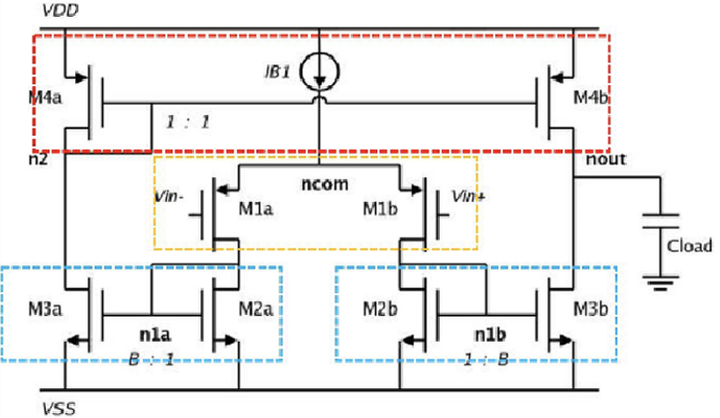

4.对如下对称OTA电路根据功能划分模块

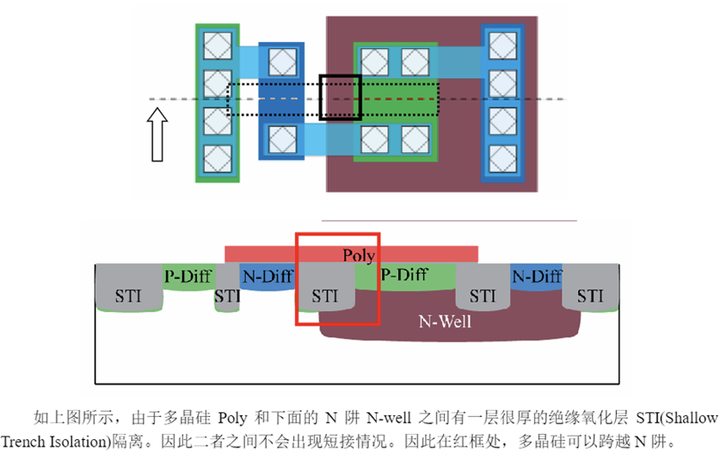

5.画出如下版图对应的如箭头方向的完整剖面图,并解释为什么多晶硅可以在黑框处跨越N阱

集成电路原理(数集)

一、名词解释45分/5分

1. 等比例缩小定律是什么,请描述你对其的理解

不知道是不是scale down的意思,在保障逻辑功能无误的情况下,先进工艺可以实现更好的能效比和性能。

2. 集成电路与电子线路的区别

3. PN结隔离介质中n+掩埋层的作用

4. 什么是平面工艺

5. 请用CMOS实现与非门,画出电路及版图

6. 什么是有比反相器与无比反相器

7. 对于与非门,若想实现最高噪声容限,则如何设计nmos、pmos的宽长比

考虑n个cmos串联的等效 Kn′ 与单个pmos的 Kp 相等即可。

8. 触发器、寄存器、锁存器的区别

9. 请给出若干ADC的性能参数及定义

简答题(最后一个5分,其他8分,共55分)

1. 画出两个增强型负载的nmos反相器,并描述其优缺点

2.画出下面这个逻辑函数的的电路图及版图(棍图)

3. 对下面这个逻辑电路化简并用cmos电路实现,建议使用最少的mos管数量

不知道能不能用传输门,笔者用的传输门,化简后仅需4个管子,但是cmos电路,不确定是不是传统的逻辑门设计思路。

4. 利用nmos传输门实现三选一电路,输入电压缺点及改进确定

5. 利用动态逻辑实现某个逻辑函数,并描述电路优点

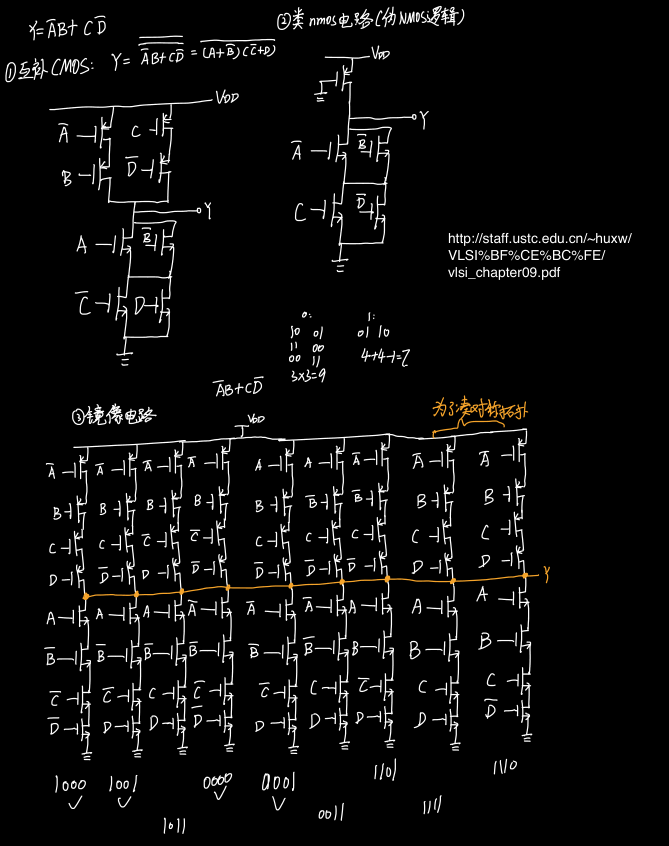

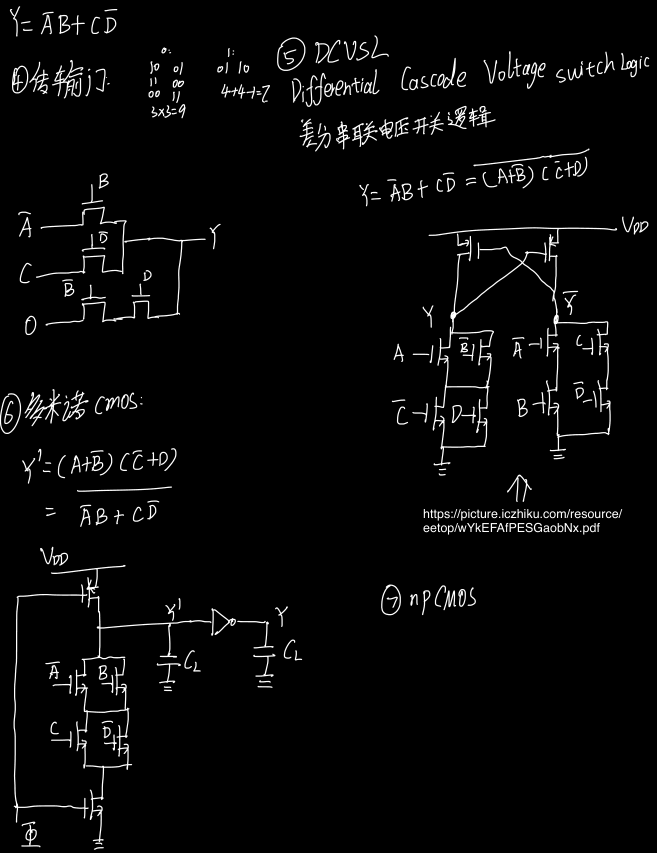

这个问题可以参考笔者撰写的这个例题的解析,对逻辑函数 Y=A¯B+CD¯ 用互补CMOS、类NMOS、镜像电路、传输门、DCVSL、多米诺CMOS设计电路。

6. Rpoly=500ohm/u方,Rmetal=5m ohm/um方,例如第二版课后题4-5+4-6

题目参数存在略微差异,不过题目大意与处理方法一致。

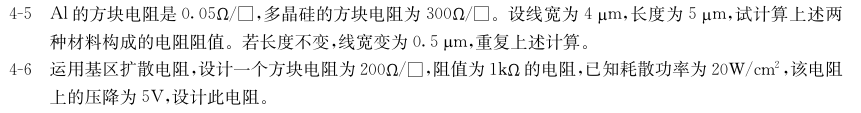

7. 利用传输门+反相器实现D触发器,描述时序逻辑,同时实现同步复位

由于时间原因,笔者未重画新图,故采用旧图展示,其中上方为同步复位,下方为异步复位。

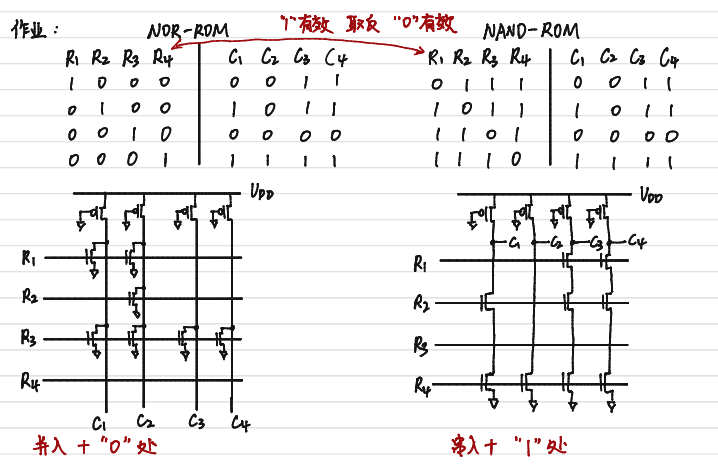

8. 根据真值表画出NAND型ROM的电路结构图

例如下图所示,该图片来自SCU模拟IC调参👑

9. 共源级放大电路的完整小信号电路,求解增益和输出电阻

SCU模拟IC调参👑认为要加入寄生电容,感觉SCU模拟IC调参👑有点严谨了,笔者就简单的小信号模型,因为没有衬偏效应,加入导通电阻 即可笔者认为。

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来源 LiMingXiang's Record!